I2C sabirnica — dodjela, uređaj, prijenos podataka, adresiranje

Prilikom izrade elektroničkog sklopa, mnogi se programeri suočavaju s potrebom korištenja velikog broja posrednih čipova za usklađivanje, uzorkovanje i adresiranje pojedinačnih blokova. Kako bi smanjio broj pomoćnih čipova, Philips je još 1980-ih predložio dvožično dvosmjerno I2C serijsko mrežno sučelje, dizajnirano posebno za upravljanje više čipova unutar jednog uređaja.

Danas samo Philips proizvodi više od stotinu I2C-kompatibilnih uređaja za elektroničku opremu sa širokim rasponom namjena: memorija, sustavi video procesora, analogno-digitalni i digitalno-analogni pretvarači, upravljački programi za zaslon itd.

I2C sabirnica je modifikacija protokola za serijsku razmjenu podataka koja može prenositi serijske 8-bitne podatke u uobičajenom "brzom" načinu rada brzinama od 100 do 400 kbps. Proces razmjene podataka ovdje je implementiran na samo dvije žice (ne računajući zajedničku žicu): SDA linija za podatke i SCL linija za sinkronizaciju.

Sabirnica postaje dvosmjerna zbog činjenice da kaskade izlaza uređaja spojenih na sabirnicu imaju otvorene kolektore ili kanale, replicirajući tako AND ožičenje. Kao rezultat toga, sabirnica smanjuje broj veza između čipova, ostavljajući manje potrebnih pinova i tragova na ploči. Kao rezultat toga, sama ploča ispada jednostavnija, kompaktnija i tehnološki naprednija u proizvodnji.

Ovaj vam protokol omogućuje da onemogućite dekodere adrese i drugu vanjsku logiku pregovaranja. Broj čipova koji mogu raditi istovremeno na I2C sabirnici ograničen je njegovim kapacitetom — maksimalno 400 pF.

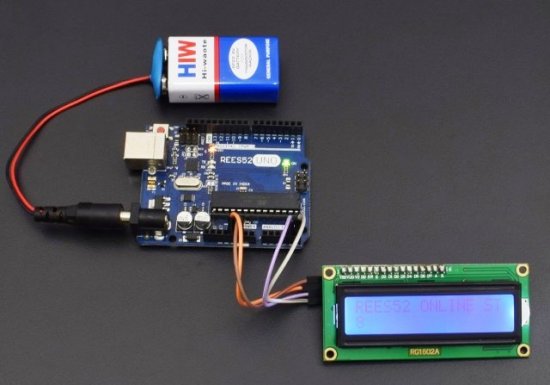

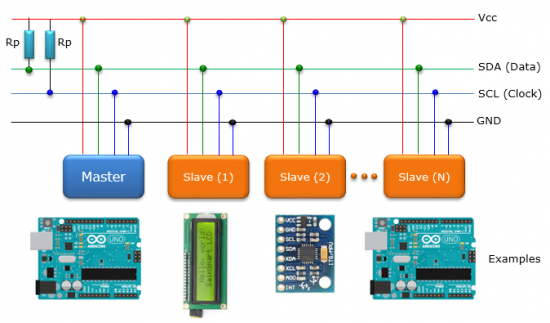

I2C-kompatibilni IC-ovi imaju hardverski algoritam za suzbijanje buke kako bi se osigurao integritet podataka čak i u prisutnosti jakih smetnji. Takvi uređaji imaju sučelje koje omogućuje međusobnu komunikaciju mikrosklopova čak i kada su im naponi napajanja različiti. Na donjoj slici možete se upoznati s principom povezivanja nekoliko mikro krugova kroz zajedničku sabirnicu.

Svaki od uređaja spojenih na sabirnicu ima svoju jedinstvenu adresu, njome je određena i, ovisno o namjeni uređaja, može raditi kao prijemnik ili kao odašiljač. Pri prijenosu podataka ovi uređaji mogu biti glavni (master) ili podređeni (slave). Master je uređaj koji inicira prijenos podataka i generira taktne signale na SCL liniji. Slave, u odnosu na master, je odredišni uređaj.

U bilo kojem trenutku rada na I2C sabirnici samo jedan uređaj može djelovati kao glavni; generira signal na SCL liniji.Master može biti ili glavni prijemnik ili glavni odašiljač.

U načelu, sabirnica dopušta nekoliko različitih mastera, ali nameće ograničenja na karakteristike formiranja upravljačkih signala i nadzora statusa sabirnice; to znači da više mastera može započeti s odašiljanjem u isto vrijeme, ali se sukobi te vrste eliminiraju zahvaljujući arbitraži, odnosno načinu na koji se master ponaša kada otkrije da je sabirnica zauzeta od strane drugog mastera.

Sinkronizacija para uređaja osigurana je činjenicom da su svi uređaji spojeni na sabirnicu, tvoreći "I" ožičenje. U početku su signali SDA i SCL visoki.

START i STOP

Razmjena počinje s masterom koji generira stanje «START»: na SDA liniji signal prelazi iz visokog u nisko stanje, dok SCL linija ima stabilnu visoku razinu. Svi uređaji spojeni na sabirnicu percipiraju ovu situaciju kao naredbu za pokretanje razmjene.

Svaki master generira individualni taktni signal na SCL liniji prilikom prijenosa podataka na sabirnici.

Razmjena završava formiranjem STOP stanja od strane mastera: na liniji SDA signal se mijenja iz niske u visoku, dok linija SCL ima stabilnu visoku razinu.

Vozač uvijek djeluje kao izvor signala START i STOP. Čim je signal «START» fiksiran, to znači da je linija zauzeta. Linija je slobodna kada se detektira STOP signal.

Odmah nakon proglašenja START stanja, glavni prebacuje SCL liniju na nisko i šalje najvažniji bit prvog bajta poruke u SDA liniju. Broj bajtova u poruci nije ograničen.Promjene na SDA liniji su omogućene samo kada je razina signala na SCL liniji niska. Podaci su valjani i ne bi se trebali mijenjati samo kada je sinkronizacijski impuls visok.

Potvrda da je podređeni prijemnik primio bajt od glavnog odašiljača vrši se postavljanjem posebnog bita potvrde na SDA liniji nakon što je primljen osmi podatkovni bit.

POTVRDA

Dakle, slanje 8 bita podataka od odašiljača do prijemnika završava s dodatnim impulsom na SCL liniji kada prijemni uređaj padne na nisku razinu na SDA liniji, što pokazuje da je primio cijeli bajt.

Potvrda je sastavni dio procesa prijenosa podataka. Master generira sinkro impuls. Odašiljač šalje nisko stanje SDA dok je sat za potvrdu aktivan. Dok je sinkronizacijski impuls visok, prijemnik mora održavati SDA niskim.

Ako odredišni podređeni uređaj ne priznaje svoju adresu, na primjer zato što je trenutno zauzet, podatkovna linija mora biti visoko postavljena. Zapovjednik tada može dati signal STOP za prekid slanja.

Ako prijem obavlja glavni prijemnik, tada je dužan obavijestiti pomoćni odašiljač nakon završetka prijenosa - ne potvrđivanjem zadnjeg bajta. Podređeni odašiljač oslobađa podatkovnu liniju tako da glavni može izdati STOP signal ili ponavljajući START signal.

Sinkronizacija uređaja je osigurana činjenicom da su veze na SCL liniju izvedene po principu "I".

Master nema isključivo pravo kontrolirati prijelaz SCL linije s niske na visoku.Ako podređeni uređaj treba više vremena za obradu primljenog bita, može samostalno držati SCL na niskom nivou dok ne bude spreman primiti sljedeći bit podataka. Linija SCL u takvoj situaciji bit će niska za vrijeme trajanja najduljeg sinkronizirajućeg impulsa niske razine.

Uređaji s najnižom održivom niskom ostat će u stanju mirovanja do kraja dugog razdoblja. Kada svi uređaji završe razdoblje niske sinkronizacije, SCL će ići na visoku razinu.

Svi uređaji počet će s visokim taktom, a prvi uređaj koji završi svoje razdoblje prvi će postaviti SCL liniju na nisku razinu. Kao rezultat toga, trajanje niskog stanja SCL-a bit će određeno najduljim niskim stanjem sinkronizacijskog impulsa jednog od uređaja, a trajanje visokog stanja bit će određeno najkraćim razdobljem sinkronizacije jednog od uređaja. uređaja.

Prijemnici mogu koristiti signale sinkronizacije kao sredstvo kontrole prijenosa podataka na razini bita i bajta.

Ako je uređaj sposoban primati bajtove velikom brzinom, ali mu je potrebno određeno vrijeme da pohrani primljeni bajt ili se pripremi za primanje sljedećeg bajta, može nastaviti držati SCL niskim nakon primanja i potvrde bajta, prisiljavajući odašiljač u stanje pripravnosti.

Mikrokontroler bez ugrađenih hardverskih sklopova, na primjer na razini bita, može usporiti brzinu takta povećanjem trajanja njihovog niskog stanja. Kao rezultat toga, brzina prijenosa glavnog uređaja bit će određena brzinom sporiji uređaj.

ADRESIRANJE

Svaki uređaj spojen na I2C sabirnicu ima jedinstvenu programsku adresu na koju mu se master obraća slanjem određene naredbe. Mikro krugove iste vrste karakterizira selektor adresa, implementiran ili u obliku digitalnih ulaza selektora, ili u analognom obliku. Adrese su podijeljene u adresni prostor uređaja spojenih na sabirnicu.

Normalni način rada pretpostavlja sedmobitno adresiranje. Adresiranje funkcionira na sljedeći način: nakon naredbe «START», master šalje prvi bajt, koji određuje koji slave uređaj je potreban za komunikaciju s masterom. Postoji i zajednička adresa poziva koja definira sve uređaje na sabirnici, svi uređaji (teoretski) na nju odgovaraju potvrdom, no u praksi je to rijetkost.

Dakle, prvih sedam bitova prvog bajta su slave adresa. Najmanji bit, osmi, označava smjer slanja podataka. Ako postoji «0», tada će se informacije pisati s mastera na ovaj slave. Ako je «1», informacije će očitati master s ovog slave.

Nakon što master završi slanje bajta adrese, svaki slave uspoređuje svoju adresu s njim. Svatko s istom adresom je slave i definiran je kao slave odašiljač ili slave prijemnik, ovisno o vrijednosti najmanjeg bita adresnog bajta.

Podređena adresa može uključivati fiksne i programabilne dijelove. Vrlo često u jednom sustavu radi veliki broj uređaja iste vrste, tada programabilni dio adrese omogućuje korištenje maksimalno iste vrste uređaja na sabirnici. Koliko se bitova u adresnom bajtu može programirati ovisi o broju slobodnih pinova na čipu.

Ponekad je dovoljan pin s analognom postavkom programabilnog raspona adresa, na primjer SAA1064 - upravljački program LED indikatora koji ima upravo takvu implementaciju. Potencijal određenog pina određuje pomak adresnog prostora čipa tako da čipovi istog tipa ne dolaze u sukob koji rade na istoj sabirnici. Svi čipovi koji podržavaju I2C sabirnicu sadrže skup adresa koje proizvođač navodi u dokumentaciji.

Kombinacija «11110XX» rezervirana je za 10-bitno adresiranje. Ako zamislimo razmjenu podataka od naredbe «START» do naredbe «STOP», to će izgledati ovako:

Ovdje su dopušteni jednostavni i kombinirani formati razmjene podataka. Kombinirani format znači da između «START» i «STOP» master i slave mogu djelovati kao prijamnici i odašiljači, ovo je korisno na primjer u upravljanju serijskom memorijom.

Neka prvi bajt podataka prenese memorijsku adresu. Zatim, ponavljanjem naredbe «START» i čitanjem slave adrese, memorijski podaci će raditi. Odluke o automatskom povećanju ili smanjenju prethodno pristupljene adrese donosi programer uređaja nakon što je prethodno proučio dokumentaciju čipa. Na ovaj ili onaj način, nakon primanja naredbe START, svi uređaji moraju vratiti svoju logiku i pripremiti se za činjenicu da će adresa sada biti imenovana.