Digitalni uređaji: flip-flopovi, komparatori i registri

Digitalni uređaji izgrađeni su na logičkim elementima, stoga se pokoravaju zakonima logičke algebre. Osnovni uređaji digitalne tehnike, uz logičke uređaje, su bistabili.

Digitalni uređaji izgrađeni su na logičkim elementima, stoga se pokoravaju zakonima logičke algebre. Osnovni uređaji digitalne tehnike, uz logičke uređaje, su bistabili.

Okidač (engleski trigger - okidač) - elektronički uređaj koji ima dva stabilna stanja i može skakati iz jednog stanja u drugo pod utjecajem vanjskog impulsa.

Okidačima ili, točnije, sustavima okidača naziva se velika klasa elektroničkih uređaja koji imaju sposobnost dugo vremena ostati u jednom od dva stabilna stanja i izmjenjivati ih pod utjecajem vanjskih signala. Svaki uvjet okidanja lako se prepoznaje prema vrijednosti izlaznog napona.

Svako stanje okidača odgovara određenoj (visokoj ili niskoj) razini izlaznog napona:

1) okidač je postavljen na jedno stanje — razina «1».

2) flip-flop je resetiran — razina «0» na izlazu.

Stacionarno stanje ostaje koliko god želite i može se promijeniti vanjskim impulsom ili isključivanjem napona napajanja. Che.flip-flop je elementarni memorijski element koji može pohraniti najmanju jedinicu informacije (jedan bit) «0» ili «1».

Flip-flopovi mogu biti izgrađeni na diskretnim elementima, logičkim elementima, na integriranom krugu ili su dio integriranog sklopa.

Glavne vrste bistabila su: RS-, D-, T-, i JK-fliperi... Osim toga, bistabli se dijele na asinkrone i sinkrone. Kod asinkronog pokretanja prebacivanje iz jednog stanja u drugo vrši se izravno dolaskom signala na informacijski ulaz. Osim podatkovnih ulaza, sinkronizirani jastabili imaju i taktni ulaz. Njihovo prebacivanje se odvija samo u prisustvu impulsa takta koji omogućuje.

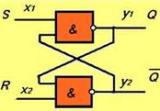

RS okidač ima najmanje dva ulaza: S (set — set) — okidač se postavlja na stanje razine «1» i R (reset) — okidač se vraća na stanje razine «0». (Sl. 1).

U prisutnosti ulaza C, flip-flop je sinkroni - prebacivanje flip-flopa (promjena stanja izlaza) može se dogoditi samo u trenutku dolaska sinkronizirajućeg (sinkronizirajućeg) impulsa na ulaz C.

Slika 1 — Konvencionalni grafički prikaz RS flip-flopa i svrha zaključaka a) asinkroni, b) sinkroni

Osim izravnog izlaza, flip-flop može imati i inverzni izlaz, čiji će signal biti suprotan.

Tablica 1 prikazuje stanja koja bistabil može zauzeti tijekom rada. Tablica prikazuje vrijednosti ulaznih signala S i R u određenom trenutku vremena tn i stanje flip-flopa (izravnog izlaza) u sljedećem trenutku vremena tn + 1 nakon dolaska sljedećeg mahunarke. Na novo stanje okidača također utječe prethodno stanje Q n.

Che.ako je potrebno napisati na okidač «1» - dajemo impuls na S ulaz, ako «0» - šaljemo impuls na R ulaz.

Kombinacija S = 1, R = 1 je zabranjena kombinacija jer je nemoguće predvidjeti kakvo će se stanje uspostaviti na izlazu.

Tablica 1 - Tablica stanja sinkronog RS flip-flopa

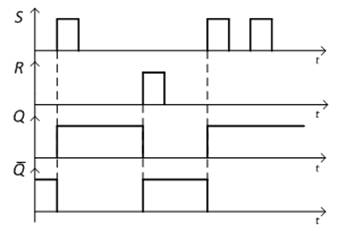

Rad flip-flopa može se vidjeti i pomoću vremenskih dijagrama (slika 2).

Slika 2 — Vremenski dijagrami asinkronog RS flip-flopa

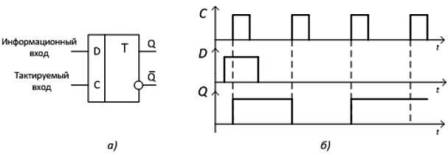

D-okidač (od engleskog delay — kašnjenje) ima jedan informacijski ulaz i taktni (sinkronizacijski) ulaz (slika 3).

D-flip-flop pohranjuje i pohranjuje na izlaz Q signal koji je bio na ulazu podataka D u trenutku dolaska taktnog impulsa C. flip-flop pohranjuje informacije zapisane kada je C = 1.

Tablica 2-Tablica stanja D-flip-flopa

Slika 3 — D -okidač: a) konvencionalni grafički prikaz, b) vremenski dijagrami rada

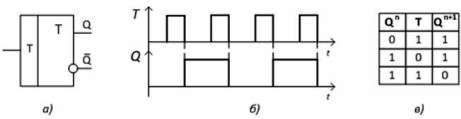

T-okidači (od engleskog tumble — prevrtanje, salto), zvani i brojački japanke, imaju jedan informacijski ulaz T. Svaki impuls (opadanje pulsa) T-ulaza (brojački ulaz) prebacuje okidač u suprotno stanje.

Slika 4 prikazuje simbologiju T-okidača (a) i vremenski dijagram rada (b).

Slika 4-T-flip-flop a) konvencionalno-grafički zapis, b) vremenski dijagram rada c) tablica stanja

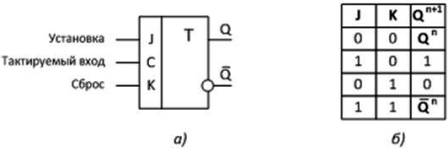

JK okidač (od engleskog jump — skok, keer — držanje) ima dva podatkovna ulaza J i K i taktni ulaz C. Dodjela pinova J i K slična je dodjeli pinova R i S, ali okidač ima nema zabranjenih kombinacija. Ako je J = K = 1, mijenja stanje u suprotno (slika 5).

Uz odgovarajuće spajanje ulaza, okidač može obavljati funkcije RS-, D-, T-okidača, tj. je univerzalni okidač.

Slika 5 - JK -flip-flop a) konvencionalni -grafički zapis, b) skraćena tablica stanja

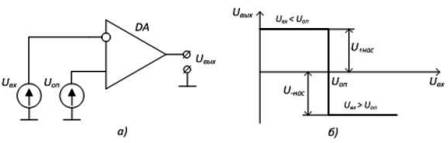

Komparator (usporedi — usporedi) — uređaj koji uspoređuje dva napona — ulaz Uin s referentnim Uref. Referentni napon je konstantan napon s pozitivnim ili negativnim polaritetom, ulazni napon se mijenja tijekom vremena. Najjednostavniji krug komparatora koji se temelji na operacijskom pojačalu prikazan je na slici 6, a. Ako je Uin Uop na izlazu U — us (slika 6, b).

Slika 6 — Op-amp komparator: a) najjednostavnija shema b) izvedbene karakteristike

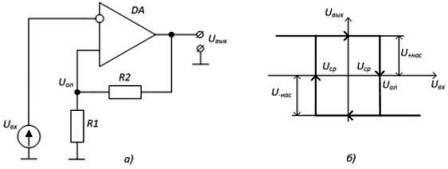

Komparator s pozitivnom povratnom spregom naziva se Schmittov okidač. Ako se komparator prebacuje s «1» na «0» i obrnuto pri istom naponu, tada Schmittov okidač - pri različitim naponima. Referentni napon stvara PIC krug R1R2, ulazni signal se dovodi na invertirajući ulaz op-amp. Slika 7, b, prikazuje prijenosnu karakteristiku Schmittovog okidača.

Pri negativnom naponu na inventarnom ulazu OS Uout = U + sat. To znači da na neinvertirajućem ulazu djeluje pozitivan napon. Kako ulazni napon raste, struja Uin > Uneinv. (Uav — okidač) komparator prelazi u stanje Uout = U -sat. Negativan napon se dovodi na neinvertirajući ulaz. Prema tome, s padom ulaznog napona u trenutku Uin <Uneinv. (Uav — okidač) komparator prelazi u stanje Uout = U + sat.

Slika 7 — Schmittov rad op-amp: a) najjednostavnija shema b) izvedbene karakteristike

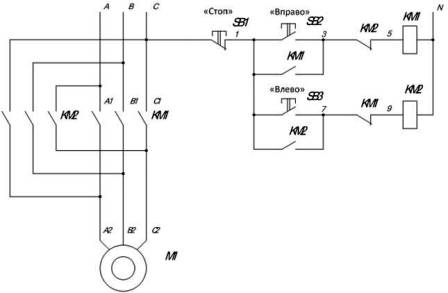

Primjer. Slika 8 prikazuje shemu relejnog kontaktora za upravljanje elektromotorom, omogućujući mu pokretanje, zaustavljanje i vožnju unazad.

Slika 8 — Shema upravljanja motorom releja i kontaktora

Komutacija elektromotora provodi se pomoću magnetskih startera KM1, KM2. Slobodno zatvoreni kontakti KM1, KM2 sprječavaju istovremeni rad magnetskih startera. Slobodno otvoreni kontakti KM1, KM2 omogućuju samozaključavanje tipki SB2 i SB3.

Da bi se poboljšala pouzdanost rada, potrebno je zamijeniti relejno-kontaktorske upravljačke krugove i strujne krugove s beskontaktnim sustavom pomoću poluvodičkih uređaja i uređaja.

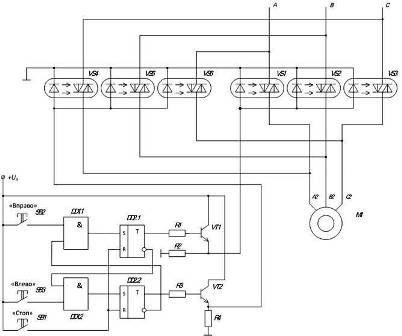

Slika 9 prikazuje beskontaktni krug upravljanja motorom.

Kontakti snage magnetskih startera zamijenjeni su opto-simistorima: KM1-VS1-VS3, KM2-VS4-VS6. Korištenje optosiistora omogućuje izolaciju upravljačkog kruga niske struje od snažnog kruga napajanja.

Okidači imaju gumbe za samozaključavanje SB2, SB3. Logički elementi I osiguravaju istovremeno aktiviranje samo jednog od magnetskih startera.

Kada se tranzistor VT1 otvori, struja teče kroz LED diode prve skupine opto-simistora VS1-VS3, čime se osigurava protok struje kroz namote motora. Otvaranjem tranzistora VT2 napaja se druga skupina opto-simistora VS4 -VS6, osiguravajući rotaciju elektromotora u drugom smjeru.

Slika 9 — Beskontaktni upravljački krug motora

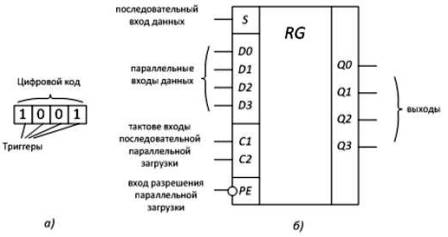

Registar - elektronički uređaj namijenjen za kratkotrajnu pohranu i pretvorbu višeznamenkastih binarnih brojeva. Registar se sastoji od flip-flopova, čiji broj određuje koliko bitova binarnog broja registar može pohraniti - veličinu registra (slika 10, a). Logički elementi mogu se koristiti za organiziranje rada okidača.

Slika 10 — Registar: a) opći prikaz, b) konvencionalni grafički zapis

Prema načinu unosa i izlaza informacija registri se dijele na paralelne i serijske.

U sekvencijalnom registru bistabili su spojeni u seriju, odnosno izlazi prethodnog bistabila prosljeđuju informaciju na ulaze sljedećeg bistabila. Ulazi C flip-flopa takta spojeni su paralelno. Takav registar ima jedan podatkovni ulaz i upravljački ulaz - satni ulaz C.

Paralelni registar istovremeno upisuje u bistabile za koje postoje četiri ulaza podataka.

Slika 10 prikazuje UGO i raspodjelu pinova 4-bitnog paralelno-serijskog registra.